# UNIVERSITY OF MASSACHUSETTS Dept. of Electrical & Computer Engineering

# Digital Computer Arithmetic ECE 666

Part 7c Fast Division – III

Israel Koren

ECE666/Koren Part.7c.1

Copyright 2010 Koren

# Speeding Up the Division Process

- ♦ Unlike multiplication steps of division are serial

- ◆ Division step consists of selecting quotient digit and calculating new partial remainder

- ◆ Two ways to speed up division:

- ♦(1) Overlapping full-precision calculation of partial remainder in step i with selecting quotient digit in step i+1

- \* Possible since not all bits of new partial remainder must be known to select next quotient digit

- ♦ (2) Replacing carry-propagate add/subtract operation for calculating new partial remainder by carry-save operation

ECE666/Koren Part.7c.2

#### First Speed-Up Method

- ♦ Truncated approximation of new partial remainder calculated in parallel to full-precision calculation of partial remainder can be done at high speed

- \* Quotient digit determined before current step completed

- ◆Instead of: (1) Calculate r<sub>i-1</sub> (with carry propagation) in step i-1 & (2) input Np most significant bits to PLA to determine q<sub>i</sub>

- Use a small adder with inputs: most significant bits of previous partial remainder, βr<sub>i-2</sub>, and most significant bits of corresponding multiple of divisor, q<sub>i-1</sub>D

- ◆ Approximate Partial Remainder (APR) adder

ECE666/Koren Part.7c.3

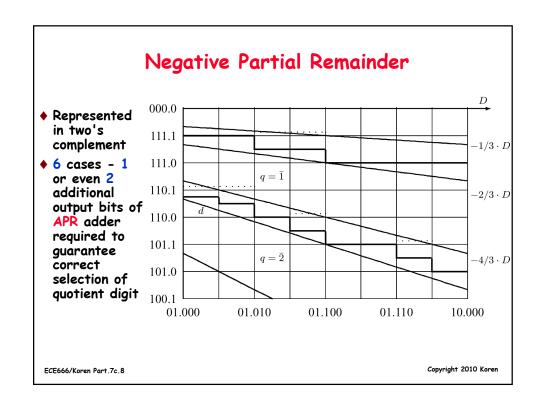

# Approximate Partial Remainder Adder

- Produces approximation of NP most significant bits of partial remainder, r<sub>i-1</sub>, before full-precision add/sub operation (r<sub>i-1</sub>=βr<sub>i-2</sub>-q<sub>i-1</sub>D) is completed

- ♦ Allows to perform look-ahead selection of qi in parallel with calculation of ri-1

- ♦ Size of APR adder determined so that sufficiently accurate NP bits generated

- Uncertainty in result of this adder larger than of truncated previous partial remainder  $\beta r_{i-2}$  may need additional inputs for quotient look-up table

- ♦8-bit APR adder sufficient to generate necessary inputs to PLA for  $\beta$ =4,  $\alpha$ =2

ECE666/Koren Part.7c.4

Copyright 2010 Koren

ADDER

$N_P$  PLA

APPROXIMATE REMAINDER

ADDER

$\stackrel{\overleftarrow{N}_P}{PLA}$

#### Second Speed-Up Method

- ♦ In first method time needed for division step determined by add/subtract for remainder quotient digit selected in previous step

- ♦ Second method avoids time-consuming carry propagation when calculating remainder

- ◆ Truncated remainder sufficient for selecting next quotient digit - no need to complete calculation of remainder at any intermediate step

- ◆ Replace carry-propagate adder by carry-save adder

- \* Partial remainder in a redundant form using 2 sequences of intermediate sum and carry bits (stored in 2 registers)

- Only most significant sum and carry bits must be assimilated using APR adder to generate approximate remainder and allow selection of quotient digit

ECE666/Koren Part.7c.9 Copyright 2010 Koren

#### SRT Divider with Redundant Remainder

APR adder

PLA

Quotient

Remainder-Carry

Remainder-Sum

Carry-save Adder

- Most time consuming calculate approximate remainder and select quotient digit

- ◆ In each division step:

carry-save adder

calculates remainder,

APR adder accepts most

significant sum and

carry bits of

remainder & generates

required inputs to quotient

selection PLA

Divisor

ECE666/Koren Part.7c.10 Copyright 2010 Koren

#### Example

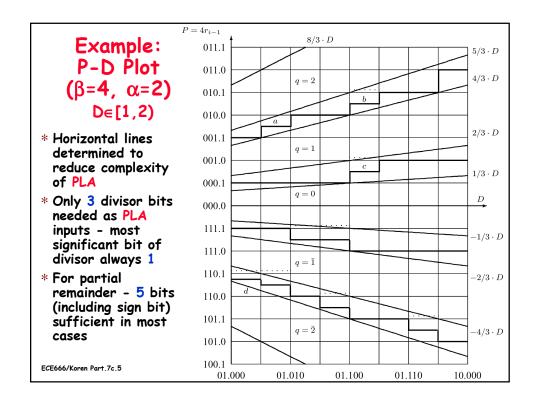

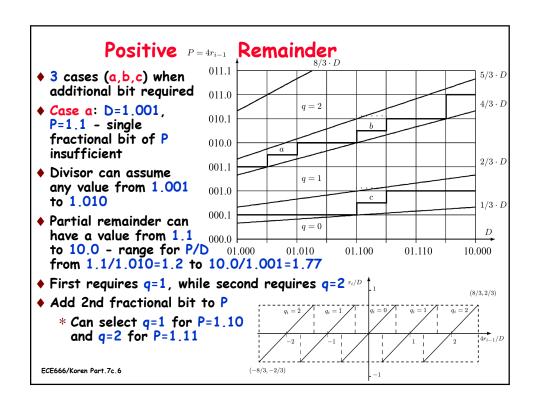

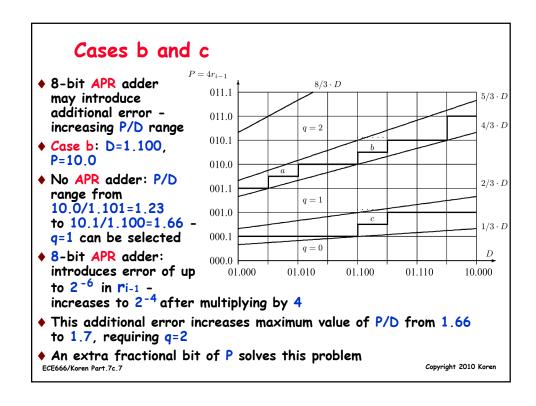

- ♦ An algorithm for high-speed division with  $\beta$ =4,  $\alpha$ =2,  $D \in [1,2)$  has been implemented

- ♦ Partial remainder calculated in carry-save manner resulting in a somewhat more complex design

- ♦8-bit APR adder used to generate most significant remainder bits inputs to quotient selection PLA

- ◆Inputs to APR adder: 8 most significant sum bits and carry bits in redundant representation of remainder

- ♦ Outputs of APR adder converted to a sign-magnitude representation only 4 bits of approximate partial remainder needed in most cases

- ◆ Additional bit required only in 4 cases simple PLA

ECE666/Koren Part.7c.11

Copyright 2010 Koren

#### Further Speed-up of SRT Division

- $\blacklozenge$  Achieved by increasing radix  $\beta$  to 8 or higher

- ◆ Reduces number of steps to \[ n/3 \] or lower

- ♦ Several radix-8 SRT dividers have been implemented

- ♦ Main disadvantage: high complexity of PLA most time-consuming unit of divider

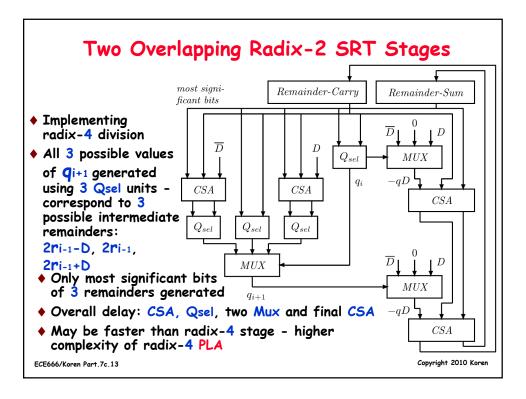

- ♦ Avoiding complex PLA implementing radix-2<sup>m</sup> SRT unit as a set of m overlapping radix-2 SRT stages

- Radix-2 SRT requires very simple quotient selection logic - qi ∈ {-1,0,1} solely determined by remainder - independent of divisor

- ♦ Must overlap quotient selections for m bits all m quotient bits generated in one step

ECE666/Koren Part.7c.12

## Extending to Radix-8 SRT division

- ♦ More complex quotient selection circuit 3 quotient digits (qi, qi+1, qi+2) generated in parallel

- ♦ For q<sub>i+1</sub>: calculate speculative remainders 2r<sub>i-1</sub>-D,2r<sub>i-1</sub>,2r<sub>i-1</sub>+D

- ♦ For qi+2: calculate 4ri-1-3D,4ri-1-2D,4ri-1-D,4ri-1,4ri-1+D, 4ri-1+2D,4ri-1+3D

- \* Only most significant bits of these 7 remainders

- ♦ 7 Qsel units required with multiplexors (controlled by qi and qi+1) to select correct value of qi+2

- ◆ Extend to 4 overlapping radix-2 stages for radix-16 divider: number of Qsel units increases from 11 to 26

- ◆ Another alternative for a radix-16 divider:

2 overlapping radix-4 SRT stages

ECE666/Koren Part.7c.14 Copyright 2010 Koren

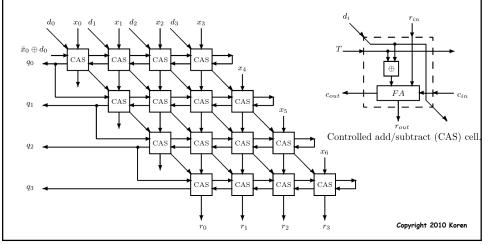

#### Array Dividers

- ♦ All division algorithms can be implemented using arrays: n rows with n cells per row for radix-2 division

- ♦ Restoring: each row forms difference between previous remainder and divisor and generates quotient bit according to sign of difference

- ♦ No need to restore remainder if quotient bit=0 either previous remainder or difference transferred to next row

- ◆If ripple-carry in every row n steps to propagate carry in a single row - total execution time of order n²

- ♦ Nonrestoring array: same speed as restoring; only advantage handle negative operands in a simple way

- ◆ Final remainder may be incorrect sign opposite to dividend

ECE666/Koren Part.7c.15

Copyright 2010 Koren

# A Non-restoring Array Divider

If T=0 (1) - addition (subtraction) performed; Subtract - add two's complement of divisor (assumed positive) & forced carry=T

#### Faster Array Dividers

- Previous array dividers add/subtract with carrypropagation performed in each row

- ♦ Nonrestoring:

- \* Only sign bit of partial remainder needed to select quotient bit

- \* Can be generated by using fast carry-look-ahead circuit

- \* Other bits of remainder use carry-save adder

- ♦ Each cell generates Pi and Gi besides sum and carry

- ◆Pi and Gi of all cells in a row connected to a carrylook-ahead circuit to generate quotient bit

- ♦ Execution time of order n log n vs. n²

- ♦ Similarly, high-radix division array with carry-save addition

- ♦ Small carry-look-ahead adder used to determine most significant bits of remainder to select quotient digit

ECE666/Koren Part 7c 17

Copyright 2010 Koren

#### Fast Square Root Extraction

- ♦ Similar to division small extensions to division unit

- ♦ Nonrestoring algorithm -

```

q_{i=1,1}; Q=0,q_1,...,q_m - calculated square root

```

- ♦ Advantages of adding 0 to the digit set of qi:

- \* Shift-only operation required when qi=0

- \* Overlap between regions of  $r_i$  where  $q_i=1$  or  $q_i=0$  are selected leads to reduced precision inspection of remainder

- Nonrestoring must identify r≥0 to correctly set qi

- \* Requires precise determination of sign bit of ri

- ◆If qi=0 allowed lower precision comparison sufficient, enables use of carry-save adders for ri

- ◆ Remainder: two sequences partial sum and carries

- ♦ Only a few high-order bits of these two sequences must be examined to select qi

ECE666/Koren Part.7c.18

#### Selection of qi=0

- ♦ Square root Q restricted to normalized fraction  $1/2 \le Q < 1$ , with  $q_1=1$

- ♦ Radicand: 1/4 ≤ X < 1</p>

- ♦ Remainder  $r_{i-1}$  ( $i \ge 2$ ):  $-2(Q_{i-1}-2^{-i}) \le r_{i-1} \le 2(Q_{i-1}+2^{-i})$  ( $Q_{i-1}$  is partially calculated root at step i-1  $Q_{i-1}=0.q_1q_2...q_{i-1}$

- ♦ In step  $i \ge 2$ , select  $q_{i=0}$  whenever  $r_{i-1}$  is in range

$$[-(Q_{i-1}-2^{-i-1}),(Q_{i-1}+2^{-i-1})]$$

♦ If qi=0, ri=2ri-1

ECE666/Koren Part.7c.19

Copyright 2010 Koren

### Selection Rule for qi

$$q_{i} = \begin{cases} 1 & \text{if} \quad r_{i-1} \geq (Q_{i-1} + 2^{-i-1}) \\ 0 & \text{if} \quad -(Q_{i-1} - 2^{-i-1}) \leq r_{i-1} \leq (Q_{i-1} + 2^{-i-1}) \\ \bar{1} & \text{if} \quad r_{i-1} \leq -(Q_{i-1} - 2^{-i-1}). \end{cases}$$

♦ Since Q<sub>i-1</sub> +2<sup>-i-1</sup> and Q<sub>i-1</sub> -2<sup>-i-1</sup> are in [1/2,1], a selection rule which avoids a high-precision comparison is

$$q_i = \begin{cases} 1 & \text{if} \quad 1/2 \le 2r_{i-1} \le 2\\ 0 & \text{if} \quad -1/2 \le 2r_{i-1} < 1/2\\ \bar{1} & \text{if} \quad -2 \le 2r_{i-1} < -1/2. \end{cases}$$

♦ Similar to the SRT rule

ECE666/Koren Part.7c.20

#### Example

**♦** X=.01111012 =61/128

| $r_0 = X$          |   | 0.0111101 |                                    |

|--------------------|---|-----------|------------------------------------|

| $2r_0$             |   | 0.1111010 | set $q_1 = 1, \ Q_1 = 0.1$         |

| $-(0+2^{-1})$ -    |   | 0.1000000 |                                    |

| $r_1$              |   | 0.0111010 |                                    |

| $2r_1$             |   | 0.1110100 | set $q_2 = 1$ , $Q_2 = 0.11$       |

| $-(2Q_1+2^{-2})$ - | 0 | 1.0100000 |                                    |

| $r_2$              |   | 1.1010100 |                                    |

| $2r_2$             | 1 | 1.0101000 | set $q_3 = \bar{1}, \ Q_3 = 0.101$ |

| $+(2Q_2-2^{-3})$ + | 0 | 1.0110000 |                                    |

| $r_3$              | 0 | 0.1011000 |                                    |

| $2r_3$             | 0 | 1.0110000 | set $q_4 = 1$ , $Q_4 = 0.1011$     |

| $-(2Q_3+2^{-4})$ - | 0 | 1.0101000 |                                    |

| $r_4$              | 0 | 0.0001000 |                                    |

| $2r_4$             | 0 | 0.0010000 | set $q_5 = 0$ , $Q_5 = 0.10110$    |

| $r_5$              | 0 | 0.0010000 |                                    |

| $2r_5$             | 0 | 0.0100000 | set $q_6 = 0$ , $Q_6 = 0.101100$   |

| $r_6$              | 0 | 0.0100000 |                                    |

| $2r_6$             | 0 | 0.1000000 | set $q_7 = 1$ , $Q_7 = 0.1011001$  |

| $-(2Q_6+2^{-7})$ - | 0 | 1.0110001 |                                    |

|                    | 1 | 0.0001111 |                                    |

♦ Square root: Q=.10110012 =89/128

$\overline{r_7}$ 1 0.0001111

◆ Final remainder:

$$2^{-7}$$

$\mathbf{r}_7 = -113/2^{14} = X - Q^2 = (7808-7921)/2^{14}$

ECE666/Koren Part.7c.21

Copyright 2010 Koren

# High-Radix Square Root Extraction

- $\bullet \beta$  radix; digit set for qi  $\{\overline{\alpha}, \overline{\alpha}, \overline{-1}, ..., \overline{1}, 0, 1, ..., \alpha\}$

- ♦ Computing new remainder:  $\mathbf{r}_i = \beta \mathbf{r}_{i-1} \mathbf{q}_i (2\mathbf{Q}_{i-1} + \mathbf{q}_i \beta^{-i})$

- ♦ Example:

$\beta=4$ , digit set  $\{\overline{2},\overline{1},0,1,2\}$  preferable - eliminates need to generate multiple 3Qi-1

- ♦ Generation of qi (2Qi-1 + qi 4<sup>-i</sup>) makes square root extraction somewhat more complex than division

- Calculation can be simplified

- ♦ For qi=1,2 subtract Q0012 & Q0102, respectively

- ♦ For  $qi=\overline{1}$  add  $Q00\overline{1}_2$  same as  $(Q-1)111_2$

- $\bullet$  For  $qi=\overline{2}$  add  $Q0\overline{10}_2$  same as  $(Q-1)110_2$

- ◆ Two registers with Q and Q-1, updated at every step, simplify execution of square root algorithm

ECE666/Koren Part.7c.22

#### Selecting Quotient Digit

- Only low-precision comparison of remainder needed to select quotient digit -

- \* Perform add/subtract in carry-save small carry-propagate adder to calculate most significant bits of ri

- \* To provide inputs to a PLA for selecting square root digit q

- \* Other inputs to PLA: most significant bits of root multiple

- Several rules for selecting q have been proposed

- \* Intervals of remainder determine size of carry-propagate adder (between 7 and 9 bits for base-4 algorithm with digits 2,1,0,1,2) and exact PLA entries

- ♦ Selected qi depends on truncated remainder and truncated root multiple

- ♦ In first step no estimated root available

- ♦ Separate PLA for predicting first few bits of root

ECE666/Koren Part 7c 23

Copyright 2010 Koren

# Example - Square Root Using Radix-4 Divider

- ♦P-D plot for divide also used for square root

- ♦ Same PLA (with 19 product terms) used for predicting next quotient digit and root digit

- ♦ A separate PLA (with 28 product terms) added

- \* Inputs 6 most significant bits of significand and least significant bit of exponent (indicates whether exponent odd or even)

- \* Output 5 most significant bits of root

$$\sqrt{1.f \cdot 2^{E-1023}} = \begin{cases} \sqrt{0.1f} \cdot 2^{(E+1)/2-1023} & \text{if } E \text{ is odd} \\ \sqrt{0.01f} \cdot 2^{E/2+1-1023} & \text{if } E \text{ is even} \end{cases}$$

♦ Radicand in [1/4,1] ⇒ square root in [1/2,1]

ECE666/Koren Part.7c.24